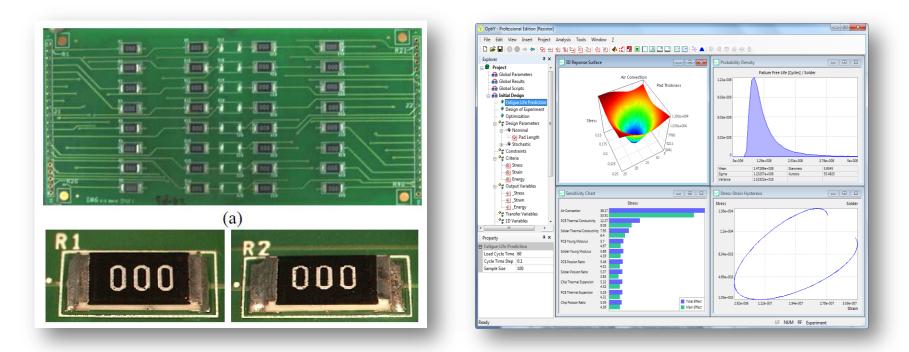

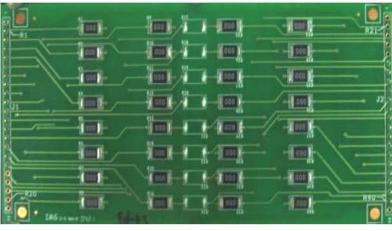

# Probabilistic Fatigue Life Prediction of Microelectronic Components on the Example of a Chip Resistor

OptiY GmbH - Germany

www.optiy.eu

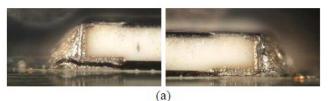

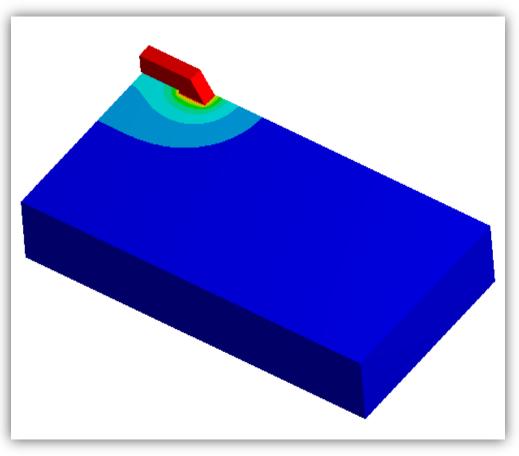

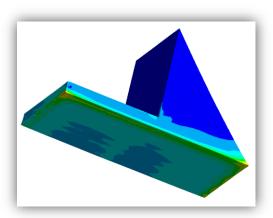

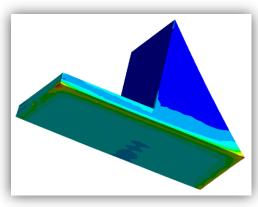

#### Failure Modes of the Chip Resistor on PCB Crack Initiation and Propagation of the Solder

(c)

www.optiy.eu

## **External FEA-Simulation**

Chip Temperature Distribution on PCB

Solder Stress Distribution

Solder Strain Distribution

www.optiy.eu

## Design, Environment and Manufacturing Parameters (Nominal and Tolerance)

| Name                        | Nominal   | Tolerance | Unit      |

|-----------------------------|-----------|-----------|-----------|

| Temperature                 | 25        | 1         | С         |

| Air Convection              | 15        | 20        | Wm^-2C^-1 |

| PCB Length                  | 40        | 1         | mm        |

| PCB Thickness               | 5         | 1         | mm        |

| PCB Width                   | 20        | 1         | mm        |

| PCB Thermal Expansion       | 1.8e-008  | 9e-010    | C^-1      |

| PCB Young Modulus           | 2.5e+010  | 1.25e+009 | Pa        |

| PCB Possion Ratio           | 0.3       | 0.015     |           |

| PCB Thermal Conductivity    | 0.294     | 0.014     | Wm^-1C^-1 |

| Pad Thickness               | 0.2       | 0.002     | mm        |

| Solder Thermal Expansion    | 2.1e-008  | 1e-009    | C^-1      |

| Solder Young Modulus        | 3e+010    | 1.5e+009  | Pa        |

| Solder Poisson Ratio        | 0.4       | 0.02      |           |

| Solder Thermal Conductivity | 124       | 6         | Wm^-1C^-1 |

| Chip Length                 | 6         | 0.1       | mm        |

| Chip Width                  | 1.5       | 0.1       | mm        |

| Chip Thickness              | 1.5       | 0.1       | mm        |

| Chip Thermal Expansion      | 2.8e-009  | 1.4e-010  | C^-1      |

| Chip Young Modulus          | 1.31e+011 | 6e+009    | Pa        |

| Chip Poisson Ratio          | 0.3       | 0.015     |           |

| Chip Thermal Conductivity   | 124       | 6         | Wm^-1C^-1 |

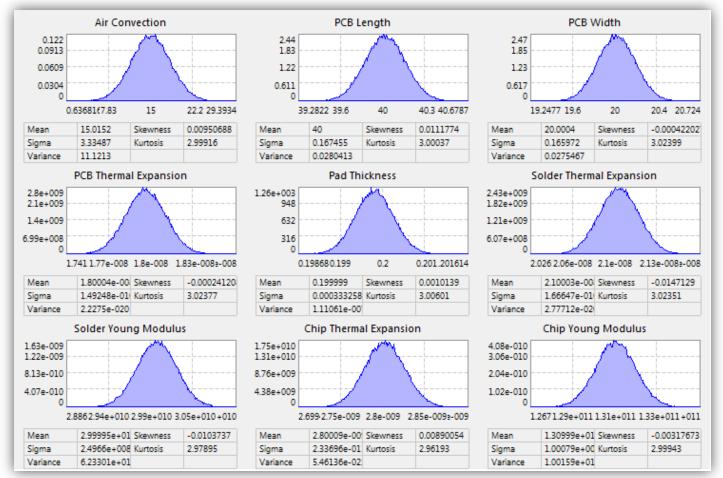

#### Parameter Uncertainties for Design, Environment and Manufacturing

www.optiy.eu

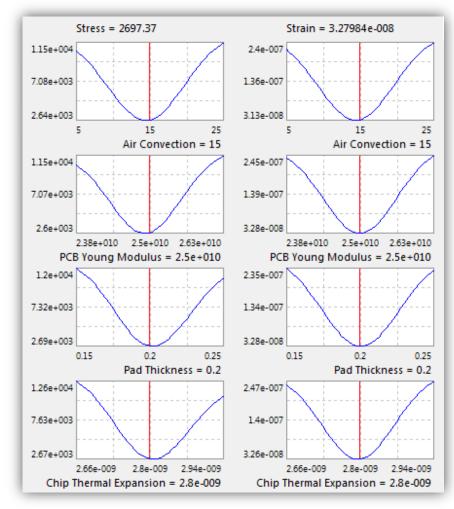

#### Meta-Models of the Solder Stress and Strain

www.optiy.eu

## Fatigue Life Model of the Solder for Relative Prediction

| Pro | Property 📧                |         |  |  |  |  |

|-----|---------------------------|---------|--|--|--|--|

| ⊡   | Strain Energy Density     |         |  |  |  |  |

|     | Name                      | Solder  |  |  |  |  |

|     | Unit                      |         |  |  |  |  |

|     | Comment                   |         |  |  |  |  |

|     | ∃ Fatigue Life Data       |         |  |  |  |  |

|     | Total Crack Length        | 1.6     |  |  |  |  |

|     | Crack Initiation Factor   | 69900   |  |  |  |  |

|     | Crack Initiation Exponent | -1.55   |  |  |  |  |

|     | Crack Growth Factor       | 0.00119 |  |  |  |  |

|     | Crack Growth Exponent     | 1.3227  |  |  |  |  |

|     | Weibull Shape Factor      | 2.6     |  |  |  |  |

|     |                           |         |  |  |  |  |

Crack Initiation:  $N_0 = K_1 * \Delta W^{K_2}$ Crack Growth:  $\frac{da}{dN} = K_3 * \Delta W^{K_4}$

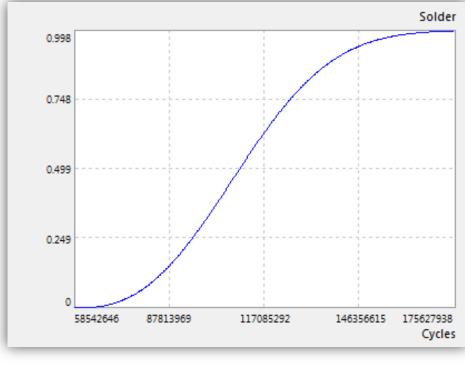

Failure Probability on Load Cycles = F(N)

$$N = N_{ff} + (\alpha_w - N_{ff})(-ln(1-F_0))^{\frac{1}{\alpha_w}}$$

$$F = 1 - exp \left[ -\left(\frac{N - N_{ff}}{\alpha_w - N_{ff}}\right)^{\beta_w} \right] \qquad \text{for N} > N_{ff}$$

www.optiy.eu

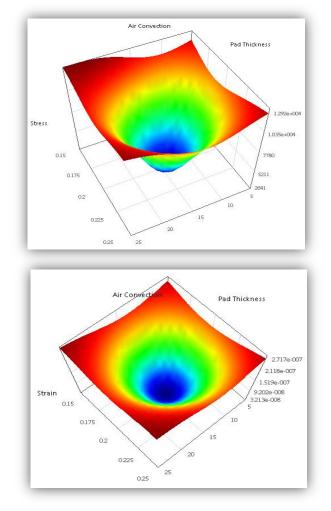

## Load Cycle of the Chip Temperature

Temperature in [°C] / Time in [Minutes]

www.optiy.eu

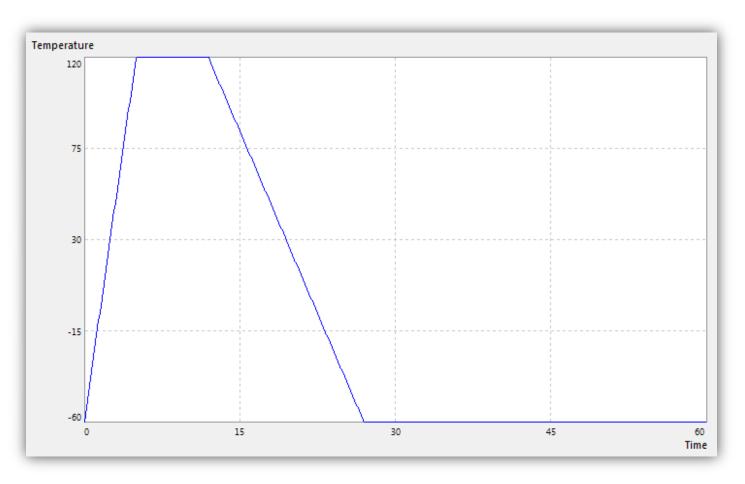

#### Stress-Strain Relationship of the Solder

www.optiy.eu

## Nominal Fatigue Life Prediction

| 📉 Fatigue Life Data         |                   |  |

|-----------------------------|-------------------|--|

| Name                        | Fatigue Life Data |  |

| Solder                      |                   |  |

| Strain Energy Density [Pa]  | 0.00835207        |  |

| Crack Initiation [Cycles]   | 116331215         |  |

| Crack Growth Rate [1/Cycle] | 2.1218e-006       |  |

| Failure Free Life [Cycles]  | 58542646          |  |

| First Failure [Cycles]      | 67223872          |  |

| 63.2% Failure [Cycles]      | 117085292         |  |

Nominal Fatigue Life Characteristics of the Resistor

Failure Free Life = 58.542.646 Cycles ( 2.439.276 Days ) Cumulative Failure Probability Distribution on the Number of Load Cycles

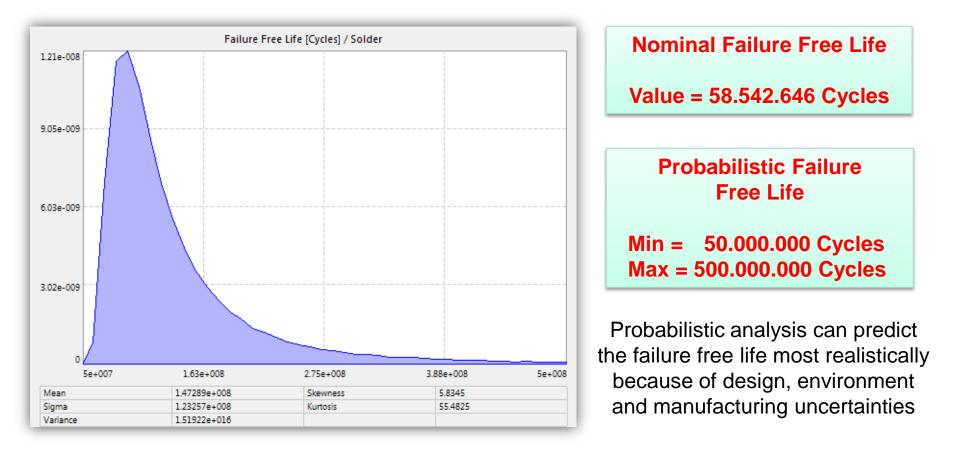

## Probabilistic Fatigue Life Prediction

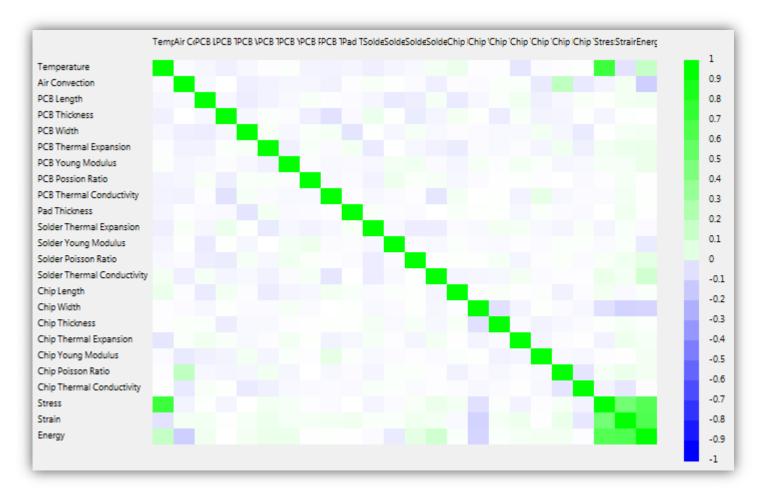

#### Linear Correlation Matrix

www.optiy.eu

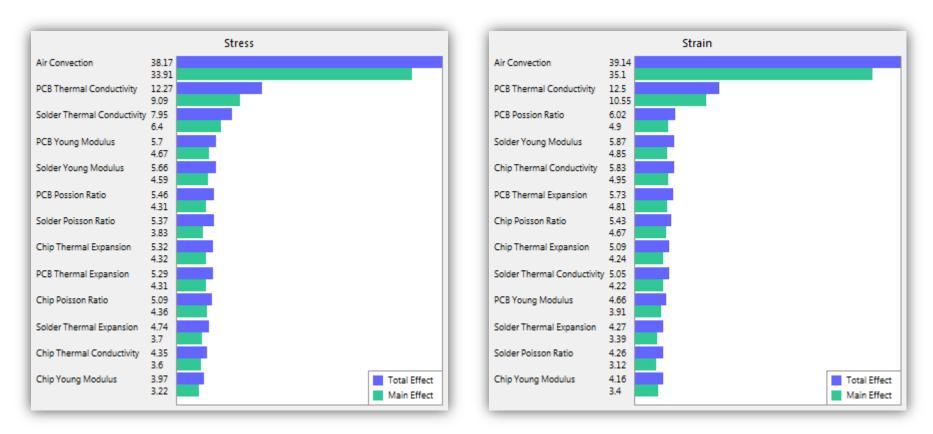

#### Sensitivity Analysis of Stress and Strain

#### Stress Sensitivity

www.optiy.eu

Strain Sensitivity

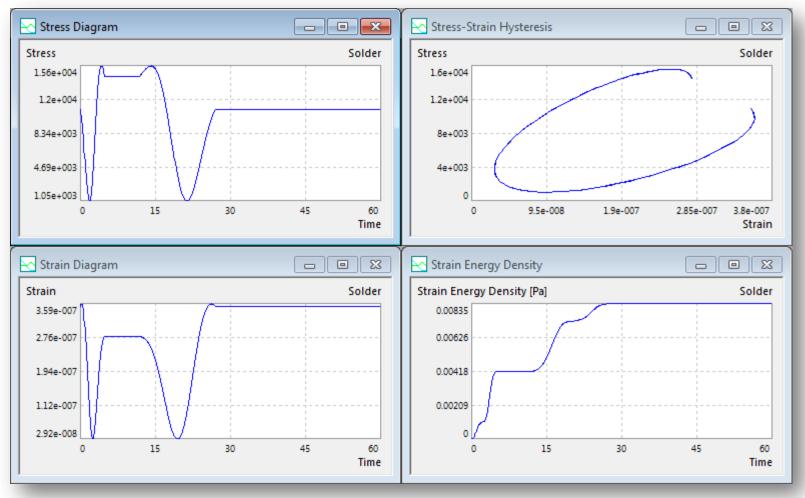

## Change the variable Design Parameters to Maximize the Nominal Fatigue Life using numerical Optimization

| Design Parameters             | Initial Design | <b>Optimized Design</b> |

|-------------------------------|----------------|-------------------------|

| X-Position Chip<br>[mm]       | 20             | 16.64                   |

| Y-Position Chip<br>[mm]       | 40             | 49.14                   |

| PCB Thickness<br>[mm]         | 5              | 6.57                    |

| Pad Thickness<br>[mm]         | 0.2            | 0.21                    |

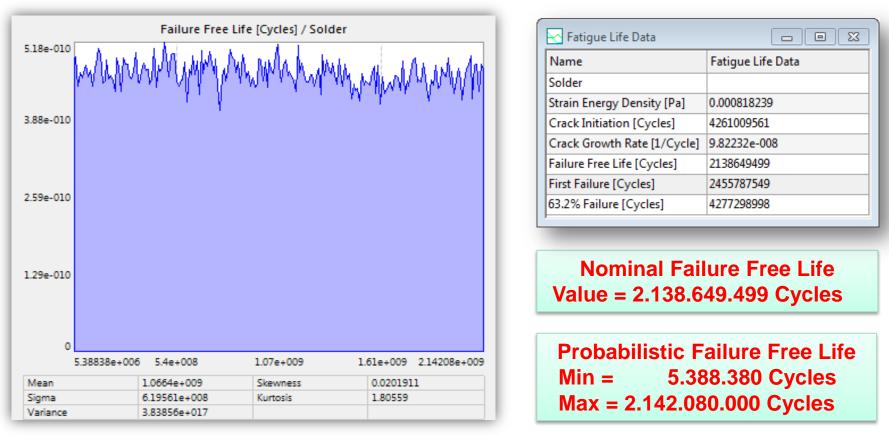

| Failure Free Life<br>[Cycles] | 58.542.646     | 2.138.649.499           |

## Design with Maximized Nominal Fatigue Life

Probabilistic analysis shows the realistic life prediction:

this design is worse than the initial design related to the min. lifetime

#### Conclusion

Nominal design using classical nominal simulation cannot warranty the reliability and quality of the products, because the nominal parameters are only one fix value.

Robust design is a power-full tool for design of reliable and quality product in the early design stage without any cost. It considers the uncertainty parameters as stochastic distributions.

In the case of the chip resistor, the probabilistic analysis using meta modeling technology can predict the realistic fatigue life related to uncertainties of design, manufacturing and environment.

**OptiY**® is the leading software platform for robust design of all engineering fields using different commercial CAD/CAE-software or in-house codes.

#### References

1. R. Darveaux: *Effect of Simulation Methodology on Solder Joint Crack Growth Correlation*. Proceedings of 50th Electronic Components and Technology Conference, Las Vegas, May 2000, pp.1048-1058

2. Pham T.Q., Kamusella A., Neubert H.: *Auto-Extraction of Modelica Code from Finite Element Analysis or Measurement Data.* 8th International Modelica Conference, 20-22 March 2011 in Dresden.

3. C. Han, B. Song: *Development of Life Prediction Model for Lead-free Solder at Chip Resistor.* 2006 Electronics Packaging Technology Conference.

4. H. L. C. Bailey: *Modeling the Fatigue Life of Solder Joints for Surface Mount Resistors*. International Symposium on Elastic Materials and Packaging (EMAP 2000), 2000.